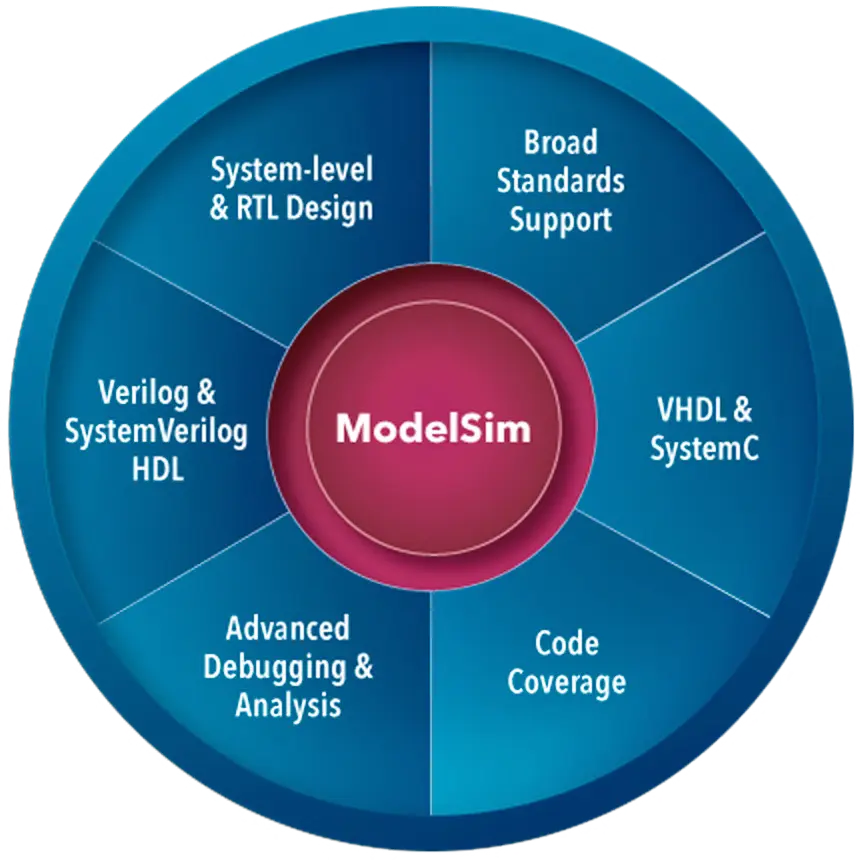

ModelSim’s award-winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design. Its architecture allows platform-independent compile with the outstanding performance of native compiled code. The graphical user interface is powerful, consistent, and intuitive. All windows update automatically following activity in any other window.

Intelligently engineered graphical user interface (GUI)

ModelSim’s intelligently engineered GUI maximizes desktop space and provides an intuitive arrangement of interactive graphical elements (windows, toolbars, menus, etc.). It enhances usability and allows for easy access to the powerful capabilities of ModelSim. Additionally, ModelSim’s integration of the Tcl scripting language further extends its openness and flexibility.

Memory Window

The memory window in ModelSim provides a user-friendly and flexible interface for viewing and debugging design memories. VHDL and Verilog memories are automatically extracted from the source code and displayed in the GUI, enabling powerful search, fill, edit, load and save functions. The memory window also supports pre-loading memories from files or using constant, random, and computed value types, eliminating the need to initialize test benches for memory loading. These features can be accessed via the command line, making them suitable for scripting and enhancing efficiency in memory-related tasks.

Waveform and Results Viewing

ModelSim offers a high-performance Wave window that provides advanced features for waveform analysis. Users can mark specific points in time using cursors and measure time distances between them. The Wave window allows flexible formatting of waveform data through virtual signal definitions and grouping, enabling easy waveform comparisons between different simulation results. ModelSim also provides time-filtering capabilities to handle timing differences between RTL and gate-level simulations. Additionally, ModelSim includes a unique WLF management utility called WLFMAN, which allows users to manipulate WLF result files, control the amount of recorded information, and efficiently manage disk space for post-simulation debugging.

Source Window Templates & Wizards

ModelSim provides VHDL and Verilog templates and wizards that simplify the development of HDL code. These tools eliminate the need to remember complex language syntax by offering pre-defined constructs that can be easily accessed with a mouse click. The user-friendly wizards guide you through the creation of more intricate HDL blocks, including parameterizable logic blocks, testbench stimuli, and design objects. Whether you’re a beginner or an experienced HDL developer, ModelSim’s templates and wizards save you time and provide convenient shortcuts for efficient code development.

Project Manager

The Project Manager streamlines file and library organization, saving you time and effort. It automatically saves the specific settings of each project, enabling you to resume simulations from where you left off. With simulation properties, you can easily re-simulate using pre-configured parameters, making the process more efficient and convenient.

Code Coverage

Code Coverage is a powerful feature in ModelSim that allows you to measure the completeness of your design verification. It supports various coverage metrics such as statement, expression, condition, toggle, and FSM coverage. These metrics are automatically derived from the HDL source code. With the ability to configure and reuse design blocks, not all metrics may be relevant. That’s why ModelSim offers flexible management of code coverage metrics using source code pragmas and exclusions specified in the code coverage browser. This feature helps ensure comprehensive verification of your design while allowing you to focus on the metrics that matter most.

Assertion Based Verification

ModelSim provides a comprehensive and standards-based solution for Assertion Based Verification (ABV). Users have the flexibility to choose between SystemVerilog Assertions (SVA), Property Specification Language (PSL), or utilize both options. This feature enhances the verification process by enabling the specification and verification of complex design properties, ensuring design correctness and reducing time-consuming manual checks.

Powerful, Cost-Effective Simulation

ModelSim offers a powerful and cost-effective simulation solution designed specifically for verifying small and medium-sized FPGA designs, particularly those with complex and mission-critical functionality. With its robust capabilities, ModelSim provides an efficient platform for accurate and thorough verification of FPGA designs, ensuring their reliability and functionality.

Platform Support

ModelSim is compatible with various platforms, including 32/64-bit Windows 10, Linux RHEL6 and RHEL7, and Linux SLES 11 and SLES 12. It operates in 32-bit mode when running on a 64-bit system, ensuring smooth performance and functionality across different platforms.